Функциональные схемы и основные электропараметры микросхем

Как отмечалось в первой статье цикла, для электрических сигналов с частотой до 1 МГц наибольшую точность преобразования обеспечивают ПСКЗ с экспоненциально-логарифмической обратной связью.

Для работы в полосе частот выше 1 МГц чаще всего применяют ПСКЗ на аналоговых умножителях (квадраторах), использующие следующий алгоритм обработки сигнала:

- Преобразование входного переменного напряжения vIN(t) в однополярный управляющий ток i(t) и последующую обработку токового сигнала. При этом исключается большое изменение напряжения в узлах и перезаряд паразитных емкостей, и быстродействие определяется в основном граничной частотой усиления транзисторов.

- Возведение управляющего тока в квадрат i2(t) и интегрирование его фильтром нижних частот (ФНЧ) с большой постоянной времени усреднения τ AV для получения среднего значения Avg(i2(t)).

- Сравнение среднего значения Avg(r2 (t)) с постоянным сигналом при помощи усилителя ошибки (error amplifier), выходное напряжение которого

- управляет цепью обратной связи (ОС) и обеспечивает выравнивание среднего значения и постоянного сигнала.

- Определение СКЗ входного сигнала по величине выходного напряжения усилителя ошибки.

Такой алгоритм реализован в преобразователях на микросхемах AD834, AD8361, AD8362, причем в AD834 и AD8361 усилитель ошибки управляет дополнительным квадратором, вырабатывающим сигнал сравнения, а в AD8362 — усилителем с регулируемым усилением в основном канале, а дополнительный квадратор обеспечивает неизменный сигнал сравнения.

Рассмотрим более подробно указанные микросхемы [1].

Функциональная схема аналогового умножителя напряжения AD834 приведена на рис. 1.

Рис. 1. Функциональная схема AD834

AD834 [2] состоит из дифференциальных каскадов (ДК) Q11, Q12 и Q13, Q14 с межэмиттерными резисторами 285 Ом для преобразования напряжения по X- и Y-входам в ток, умножающего блока на основе ячейки Джильберта (Gilbert cell) Q1-Q6 [3] и усилителя тока Q7-Q10 с коэффициентом передачи ≈1,6. Для стабилизации токового смещения ДК при изменении температуры и напряжения питания применяется источник опорного напряжения, определяемого шириной запрещенной зоны (bandgap reference) [4]. Внутри умножителя происходит обработка только токового сигнала, что определяет большую полосу пропускания, высокую воспроизводимость и стабильность параметров, при этом максимальную погрешность умножения напряжения по X- и Y-входам вызывает нелинейность преобразования напряжения в ток дифференциальными каскадами [5]. Для уменьшения этой нелинейности в AD834 введены блоки компенсации искажений (distortion cancellation). Лазерной подгонкой номиналов резисторов при измерении AD834 на полупроводниковой пластине обеспечивается высокая точность выполнения функции преобразования (transfer function) умножителя:

IW = KVIVXVY (1)

где IW — дифференциальный выходной ток, протекающий от вывода W1 к W2, VX =VX1 –VX2 — дифференциальное входное напряжение между выводами X1, X2, VY =VY1 –VY2 — дифференциальное входное напряжение между выводами Y1, Y2, KVI — коэффициент преобразования умножителя с размерностью А/В2.

В AD834 максимально допустимое входное дифференциальное напряжение (Full Scale — FS) по X- и Y-входам составляет ±1 В, а KVI = 4 мА/В2.

ПСКЗ на основе умножителя AD834 показан на рис. 2.

Рис. 2. ПСКЗ на умножителях AD834

Входной сигнал в ПСКЗ поступает на параллельно соединенные X- и Y-входы умножителя M1 через сдвоенный резистивный делитель, который обеспечивает входное сопротивление ПСКЗ равное 50 Ом, при этом в 2 раза увеличивает диапазон допустимого входного дифференциального напряжения, до ±2 В FS. Кроме того, последовательное соединение с входом ИС резистора небольшой величины уменьшает влияние паразитной индуктивности корпуса и выравнивает амплитудно-частотную характеристику (АЧХ).

Входной ток смещения умножителя (≈45 мкА), протекая по параллельно соединенным с каждым входом Y1, X2 двум резисторам величиной 50 Ом, создает падение напряжения 1,125 мВ, которое может вызвать появление выходного сигнала M1 при отсутствии входного. Для компенсации влияния тока смещения входы Y2 и X1 соединены с нулевым потенциалом через резисторы 25 Ом. В этом случае аддитивная погрешность определяется разностью входных токов смещения и поэтому значительно меньше. Как и для всех высокочастотных ИС, напряжение питания умножителей фильтруется RC-цепями: 10 Ом, 158 Ом, 1 мкФ. Кроме того, включение резистора 158 Ом между положительным источником напряжения +6 В и выводом +VS микросхемы позволяет уменьшить напряжение на базах выходных транзисторов умножителя Q9, Q10 до 6 В–158 ОмK11 мА= =4,262 В, где 11 мА — ток потребления AD834 по выводу +VS, и исключить насыщение Q9, Q10 при максимально возможном выходном сигнале, при котором напряжение VWMIN на коллекторах Q9, Q10 (вывод W1, W2) составит примерно 6 В – (8,5+4) мАK100 Ом = 4,75 В.

При параллельном соединении X- и Y-входов умножитель работает как квадратор и его дифференциальный выходной токовый сигнал

iW = KVI(vY1 – vX2)2 (2)

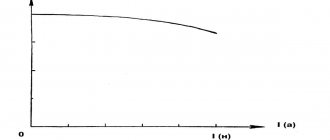

преобразуется в напряжение на 100-омных резисторах, образующих совместно с конденсаторами величиной 4,7 мкФ и 0,01 мкФ основной ФНЧ. Дополнительную фильтрацию нижних частот осуществляет операционный усилитель A1 (усилитель ошибки) с конденсаторами, соединенными с его входами.

Если постоянная времени усреднения фильтра τAV ≈ 4,7 мкФK100 Ом = 0,47 мс намного больше, чем период входного сигнала, то дифференциальное напряжение между выходами M1 (vW1 – vW2) эффективно усредняется и поступает на входы усилителя А1 через сдвоенный резистивный делитель, предназначенный для сдвига уровня. Выходное напряжение А1 через эмиттерный повторитель управляет квадратором M2 в цепи отрицательной обратной связи. Умножитель M2 применяется с входным резистивным делителем для того, чтобы согласовать максимальное выходное напряжение ПСКЗ +2 В FS c допустимым диапазоном микросхемы AD834, равным +1 В FS. Следует заметить, что выход W1 (W2) умножителя M1 соединен с выходом W2 (W1) умножителя M2, поэтому выходные токовые сигналы M1 и M2 в противофазе, то есть вычитаются. Отрицательная обратная связь устанавливает такое выходное напряжение ПСКЗ, при котором входное дифференциальное напряжение А1 близко к нулю:

где V+, V– — напряжение на неинвертирующем и инвертирующем входе А1, K — коэффициент передачи резистивного делителя, соединяющего выходы умножителей M1, M2 c входами усилителя A1, K= 0,85 для номиналов резисторов на рис. 2, iWM1, iWM2 — дифференциальный выходной ток умножителя M1, M2 соответственно, vIN, VOUT — входное и выходное напряжение ПСКЗ соответственно.

Рис. 2. ПСКЗ на умножителях AD834

В (3) предполагается, что умножители M1 и M2 имеют одинаковый коэффициент преобразования KVI . Так как

преобразуется в напряжение на 100-омных резисторах, образующих совместно с конденсаторами величиной 4,7 мкФ и 0,01 мкФ основной ФНЧ. Дополнительную фильтрацию нижних частот осуществляет операционный усилитель A1 (усилитель ошибки) с конденсаторами, соединенными с его входами.

ПСКЗ на основе AD834 имеет ряд особен- ностей:

- Применение биполярного напряжения питания позволяет по X- и Y-входу умножителя обрабатывать двухполярные сигналы около нулевого напряжения. При этом допустимо соединение умножителя M1 с источником входного сигнала без разделительного конденсатора и преобразование переменных сигналов с постоянной составляющей.

- Погрешность ПСКЗ определяется в большей степени нелинейностью преобразования напряжения в ток во входных ДК-умножителях (транзисторы Q11-Q14) и напряжением смещения M1, M2, A1, особенно умножителя M2 в цепи обратной связи. Нелинейность можно значительно уменьшить при увеличении максимального падения напряжения на межэмиттерном резисторе транзисторов Q11, Q12 (Q13, Q14) [5] или введением блоков компенсации искажений. Оба этих способа приводят к увеличению минимального напряжения питания, поэтому AD834 имеет диапазон допустимого входного дифференциального сигнала ±1 В FS и нелинейность менее 0,3% при напряжении питания ±5 В.

- Для уменьшения погрешности преобразования ПСКЗ умножители M1 и M2 должны иметь одинаковые коэффициенты преобразования KVI, чего легко достичь при изготовлении сдвоенных умножителей на одной полупроводниковой подложке.

- Из-за конечного значения времени усреднения основного ФНЧ на выходе ПСКЗ будут пульсации напряжения с удвоенной частотой входного сигнала. Эти пульсации можно уменьшить увеличением τAV или дополнительной фильтрацией усилителем А1 с частотно-зависимой обратной связью, поэтому в качестве А1 желательно применять самые низкочастотные ОУ, например микромощные.

- Дополнительная погрешность 1% в области высоких частот f–1%H ПСКЗ определяется полосой пропускания и идентичностью фазовых характеристик по X- и Y-входу умножителя M1 (одинаковые задержки распространения сигнала), а также паразитной индуктивностью выводов корпуса.

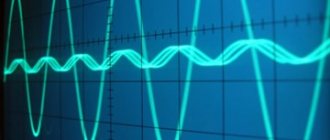

В микросхеме AD834, собранной в 8-вывод- ной корпус типа Cerdip (Q), из-за влияния па- разитной индуктивности АЧХ (начиная с час- тоты 70 МГц) имеет подъем, который достигает максимума около 800 МГц, а затем начинается спад. Для других типов корпусов форма АЧХ такая же, но отличается частота начала подъема и максимума АЧХ. Соединение последовательно с входом небольшого гасящего резистора (damping resistor) значительно уменьшает пик АЧХ и делает ее более равномерной, однако конкретная величина гасящего резистора зависит от топологии печатной платы и корпуса микросхемы.

Следует заметить, что для AD834 полоса пропускания (bandwidth-BW) нормируется при измерении среднего квадрата входного напряжения без последовательно соединенных с входом резисторов. Такое вклю- чение описывает наихудший режим эксплуатации, так как учитывает все факторы: полосу пропускания, фазовую неидентичность каналов, паразитную индуктивность корпуса.

Основным недостатком ПСКЗ, показанного на рис. 2, является боль- шая рассеиваемая мощность, которая только для одного умножителя AD834 составляет 11 мАxK4,262 В + 28 м x АK6 В = 215 мВт.

В отличие от рассмотренного ПСКЗ на умножителях AD834, микро- схема AD8361 (рис. 3–4) представляет собой функционально закончен- ный и не требующий дополнительных активных элементов определи- тель средней мощности (mean power detector) высокочастотных сиг- налов различной формы.

Рис. 3. Функциональная схема AD8361

Рис. 4. Типовая схема включения AD8361

Функциональная схема AD8361 очень близка к схеме, показанной на рис. 2, за исключением:

- Квадраторы на умножителях с параллельно соединенными X- и Y- входами заменены одновходовыми квадраторами, выходной ток которых пропорционален квадрату входного напряжения (transconductance cell) i = KVIv2IN.

- Вместо эмиттерного повторителя введен дополнительный буферный усилитель с небольшим усилением (x7,5_BUFFER), при этом напряжение постоянного тока по выводу VRMS линейно зависит от СКЗ напряжения переменного тока по входу RFIN с коэффициентом преобразования, равным 7,5 В/ВСКЗ.

- В источнике опорного напряжения (bandgap reference) имеется возможность отключения питания микросхемы управляющим сигналом— режим «power down». При подаче на вывод PWDN положительного напряжения питания VPOS ток потребления ИС при отсутствии входного сигнала уменьшается от 1,1 мА до

- Постоянное выходное напряжение VRMS по выводу VRMS при отсутствии сигнала по входу RFIN VRFIN = 0 можно задавать различным соединением выводов IREF (internal reference — внутреннее смещение) и SREF (supply reference — смещение, определяемое напряжением питания): VRMS = 0, если IREF соединен с VPOS, SREF соединен с нулевым потенциалом (Ground Referenced Mode); VRMS ≈ 350 мВ, если IREF «оборван», SREF соединен с нулевым потенциалом (Internal Referenced Mode); VRMS = VPOS/7,5, если IREF и SREF соединен с VPOS (Supply Referenced Mode).

- Внутри ИС имеется конденсатор фильтра нижних частот (INTERNAL_FILTER), но время усреднения можно увеличить подключением внешнего конденсатора между выводами VPOS и FLTR, при этом уменьшаются пульсации напряжения по выводу VRMS.

Хотя фирмой Analog Devices указывается, что микросхема AD8361 ра- ботоспособна в широком диапазоне частот, от низких до 2,5 ГГц, но вну- тренняя структура и уровень электропараметров ИС рассчитаны скорее на высокочастотную область. Напряжение питания ИС является одно- полярным и может лежать в диапазоне от 2,7 В до 5,5 В. Благодаря это- му значительно уменьшена потребляемая мощность, но однополярное напряжение питания приводит к существованию постоянного напря- жения ≈0,8 В на входе RFIN относительно вывода COMM. В связи с этим вход RFIN может соединяться с источником сигнала только через раз- делительный конденсатор CC. Разделительный конденсатор CC совме- стно с согласующим резистором (R1 на рис. 4) или входным сопротив- лением ИС по выводу RFIN, равным 225 Ом, образуют фильтр верхних частот (ФВЧ), не позволяют обрабатывать сигналы с постоянной состав- ляющей и значительно увеличивают погрешность преобразования низ- кочастотного сигнала. Малая величина напряжения питания также не раз- решает повысить линейность преобразования входного напряжения в ток, в результате чего увеличивается погрешность СКЗ-преобразова- ния. Другими источниками погрешности являются шумы при мини- мально возможном сигнале и отклонение функции преобразования ква- дратора от квадратического закона при максимальном.

Для AD8361 погрешность на частоте 100 МГц составляет ≈3 % в ди- апазоне изменения входных сигналов 14 дБ, что явно недостаточно для метрологических применений.

Динамический диапазон (dynamic range — DR) по входу микросхе- мы ограничен напряжением питания и выбранным коэффициентом преобразования. Допустимое выходное напряжение (output swing) AD8361 на несколько милливольт больше нулевого напряжения и примерно на 100 мВ меньше напряжения питания VPOS, поэтому при VPOS = 5 В максимально допустимое входное напряжение будет vINPMAX = 4,9 В/7,5 = 653 мВСКЗ.

В модернизированной микросхеме AD8362 по сравнению с AD8361 входной динамический диапазон существенно расширен (до 60 дБ), но остальные недостатки AD8361 остались.

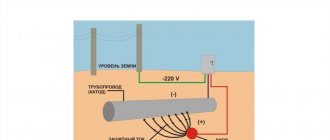

ИС AD8362, функциональная схема которой показана на рис. 5, состоит из:

Рис. 5. Функциональная схема AD8362

- Широкополосного усилителя с изменяемым усилением (variable gain amplifier –VGA), усиление которого GSET может устанавливаться при помощи специального интерфейса (setpoint interface) в диапазоне от –21 до +39 дБ в зависимости от напряжения на выводе VSET:

где G0 — фиксированное усиление при VSET = 0, VGNS — масштабирующее напряжение, определяющее наклон зависимости GSET от управляющего напряжения VSET.

При этом выходное напряжение vSIG усилителя VGA будет равно

где vIN — переменное напряжение на входе AD8362, оно может быть подано на вывод INHI при заземленном INLO или между выводами INHI и INLO.

Усилитель VGA имеет цепь компенсации напряжения смещения (offset NULLing), которая делает АЧХ усилителя подобной ФВЧ (фильтр верхних частот — high pass filter) с частотой среза в области низких частот fHP . Частота среза fHP должна быть значительно меньше рабочей частоты. Ее величина определяется конденсатором, соединенным с выводом CHPF:

- Источника опорного напряжения (bandgap reference), задающего режим работы всех блоков ИС и имеющего выход VREF с напряжением VREF =1,25 В.

- Аттенюатора с коэффициентом передачи 0,06 и входами VTGT и ACOM, напряжение VTGT между которыми устанавливает амплитудную цель (amplitude target) для напряжения VSIG . Если VTGT соединен с VREF, а ACOM заземлен, то напряжение на выходе аттенюатора VATG = 0,06 x 1,25 В = 75 мВ.

- Двух согласованных по параметрам широкополосных квадраторов (match wide-band squares) с выходным током, пропорциональным квадрату входного напряжения

В отличие от рис. 3, на котором сравнение сигналов квадраторов проводится путем преобразования их выходных токов в дифференциальное входное напряжение усилителяошибки, в AD8362 квадраторы имеют разное направление выходного тока: ток iSQU — вытекающий, а iTGT — втекающий. При прямом соединении выходов квадраторов разностный выходной ток будет протекать через внутренний фильтрующий конденсатор CF и внешний конденсатор CLPF, подключенный между выводами CLPF и ACOM. Конденсатор CLPF определяет частоту среза в области высоких частот ФНЧ (фильтр нижних частот — low pass filter) fLP . Рекомендуемая величина для режима измерений (рис. 6) CLPF = 300 пФ, а для работы в низкочастотной области

- Не инвертирующего усилителя выходного фильтра (OUTPUT_FILTER), выход которого соединен с выводом VOUT, а внутренними резисторами установлен коэффициент передачи, равный 5 (internal resistors set buffer gain to 5).

Очевидно, что внутренняя структура AD8362 довольно универсальна и позволяет реализо- вать различные функции, поэтому рассмот- рим только включение ИС для режима изме- рения переменного напряжения, как показано на рис. 6.

Рис. 6. Схема включения AD8362 для измерения переменного напряжения

Входы INHI, INLO микросхемы AD8362 имеют постоянное смещение ≈3,6 В относительно вывода ACOM и входное сопротивление ≈100 Ом, поэтому их непосредственное соединение с источником сигнала недопустимо и требуется применение разделительных конденсаторов СCPL . Кроме того, рекомендуется подключение конденсаторов CDECL на развязывающие выводы (decoupling terminals) DECL микросхемы.

В режиме измерения переменного напряже- ния постоянный ток iTGT задается соединени- ем выводов VTGT и VREF, а усиление GSET оп- ределяется напряжением VOUT, подаваемым на вывод VSET. Конденсаторы CF и CLPF заря- жаются переменным током iSQU и постоянным iTGT до напряжения VCF, которое усиливается в 5 раз, поступает на вывод VOUT, VSET и уп- равляет усилением GSET. Если заряд конденса- торов СF и СLPF током iSQU больше, чем разряд током iTGT, то напряжение VCF и VOUT увели- чивается и, как следует из (5), GSET уменьша- ется и уменьшает iSQU . Такая отрицательная обратная связь приводит к тому, что устано- вится следующий режим работы:

Avg(iSQU) = iTGT (11)

Если квадраторы имеют одинаковый коэф- фициент преобразования, то

Avg(v2SIG) = V2ATG (12)

или с учетом (6)

где VZ =VATG/G0 — СКЗ входного напряжения, при котором VSET должно равняться нулю при выполнении зависимости (14), то есть VSET =0 при

Для режима измерения переменного напряже- ния VSET = VOUT . Учитывая это и заменив в (14) натуральный логарифм на десятичный, получим:

где VSLP = VGNS x KLn(10) = 2,303 x VGNS — коэф- фициент преобразования, то есть изменение выходного напряжения постоянного тока при изменении СКЗ входного напряжения переменного тока на декаду (10 раз или 20 дБ). Для AD8362 лазерной подгонкой сопротивлений на пластине установлено для частоты 100 МГц изменение выходного напряжения на 1 В при изменении СКЗ входного напряжения в 10 раз (1 В/20 дБ или 50 мВ/дБ), а также установлено VZ = 316 мкВ.

Непосредственное сравнение ПСКЗ на ми- кросхемах AD834, AD8361, AD8362 затрудне- но, так как параметры ПСКЗ не нормируются изготовителем ИС, а зависят от конкретной реализации ПСКЗ потребителем: топологии и качества печатной платы, выбранных типов и номиналов внешних элементов, согласова- ния с источником входного сигнала и пр. В таблице приведены только основные харак- теристики микросхем AD834, AD8361, AD8362, определяющие параметры ПСКЗ.

Таблица. Основные характеристики микросхем на аналоговых умножителях

Общая информация

Под преобразователем понимают электротехнический прибор, способный преобразовать электроэнергию, имеющую одни параметры, в электроэнергию с другими параметрами.

В качестве параметров рассматриваются: ток, напряжение, фаза.

Преобразователи классифицируют на:

- управляемый и неуправляемый, то есть на выходе параметры либо регулируются, либо нет

- электромашинный (вращающийся) и полупроводниковый (статический), который бывает диодным, тиристорным и транзисторным

- выпрямитель, инвертор, преобразователь частоты, регулятор напряжения переменного или постоянного тока, фазовый преобразователь

Наиболее распространенной моделью преобразователя, на сегодняшний день, является полупроводниковый тиристорный или транзисторный преобразователь. Это обуславливается рядом преимуществ и функциональных возможностей, таких как: высокое быстродействие и КПД, длительный срок эксплуатации, простота в обслуживании и использовании.

Подобные преобразователи имеют и ряд недостатков. Например они чувствительны к перегрузкам тока и напряжения.

Устройство прибора

Преобразователи напряжения не обходятся без следующих комплектующих элементов:

- ключевого коммутирующего элемента

- источника питания

- индуктивного накопителя питания

- фильтра-конденсатора

- блокировочного диода

В зависимости от порядка включения и сочетания каждого из перечисленных выше элементов, создается инвертирующий преобразователь, повышающий или понижающий.

Принцип работы

Преобразователи напряжения (инверторы), обеспечивая максимальное значение коэффициента полезного действия, вырабатывают напряжение, величина которого необходима для питания определенного вида аппаратуры. Трансформатор выступает как промежуточный элемент, который временно переводит напряжение из постоянного значения в переменное.